An innovative hybrid circuit for quantum computers

17 June 2019

Contributing towards the realization of practical large-scale quantum computers by reducing architectural complexity.

Researchers at University College London, together with colleagues at University of Cambridge, CEA-LETI and Hitachi Cambridge Laboratory just published today on Nature Electronics a demonstration of a hybrid electronic circuit to address a barrier to realizing a practical large-scale quantum computer. Inspired by dynamic random-access memory (DRAM) architecture, the hybrid electronic circuit combines conventional and quantum devices on a chip using complementary metal-oxide semiconductor (CMOS) technology, to deliver input and output signals to quantum processors while keeping the number of connections manageable, and thereby reduce the complexity of quantum computing architecture. This innovation represents another milestone in current worldwide efforts for the realization of a practical large-scale fault-tolerant quantum computer.

Quantum computers promise to solve some of the most challenging computational problems such as simulation for revolutionary new materials, chemicals and medicines. However, to tackle the most demanding computational simulations, it is thought that a large-scale fault-tolerant quantum computer might ultimately require 10 million quantum bits (qubits) to run the most complex of calculations - a much larger number than what current technology can support. In the quest to build that large-scale quantum computer, one important challenge is how to reduce the complexity of the quantum computing architecture. This challenge involves, for example, efficient management of the input and output (I/O) of data and the reduction of circuit elements.

To address the “I/O problem,” the team used CMOS technology to fabricate a hybrid circuit that combines digital, analogue and quantum devices all operating at 10 milikelvin. The circuit which contains quantum devices interfaced by digital transistors simplifies the processor architecture as it enables efficient routing of the readout signals and reduces the number of sensors for readout. The team demonstrated that these circuits can be used to efficiently route signals to the quantum devices. Furthermore, with this circuit, the team showed how to reduce the number of sensors required for readout, by dynamically connecting the quantum devices to a single readout resonator. The concept, inspired by conventional DRAM architecture will mean an overall simplification of the quantum computer and using CMOS for quantum computing will lead to a reduction of the production cost and facilitate commercialization at scale in the future.

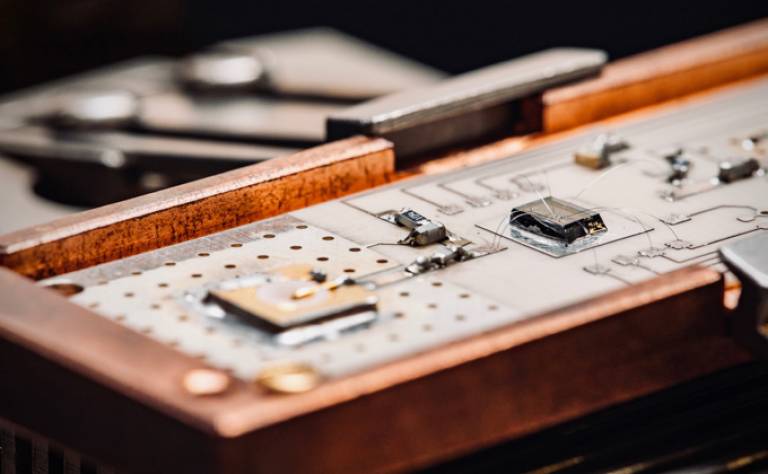

IMAGE CAPTION: CMOS hybrid circuit used to perform the experiment. The chip contains two cells, each composed of one control transistor and one quantum device. Credit: A.Abrusci, UCL.

MEDIA CONTACT: Agnese Abrusci, UCL Quantum Science and Technology Institute

Close

Close